# **RA8873ML4N**

# Character/Graphic TFT LCD Controller

**Datasheet**

December 27, 2017

RAiO Technology Inc.

©Copyright RAiO Technology Inc., 2017

#### 1. Introduction

This is the Hardware Functional Specification for the RA8873M TFT LCD Controller. RA8873M supports CMOS type interface. Including in this document are system block diagrams, Pin information, AC/DC characteristics, each block's function description, detail register descriptions, and power mode control.

#### 1.1 Overview Description

RA8873M is a low-cost color TFT LCD controller for the small and the medium-size panel, the RA8873M have Buffer RAM, The RA8873M supports an 8/16-bit asynchronous parallel host bus while providing high performance bandwidth into the display memory allowing for fast screen updates.

The RA8873M also provides support for multiple display buffers, Picture-in-Picture, Opacity control, and display rotation/mirror ... etc.

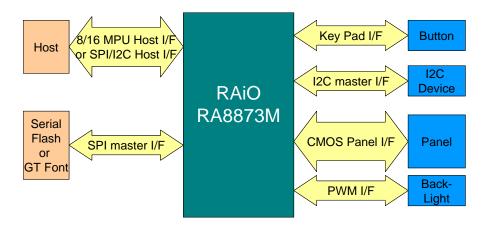

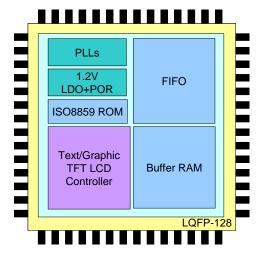

#### 1.2 System Diagram & Chip Diagram

Figure 1-1: System Diagram

Figure 1-2: Chip Diagram

#### 2. Features

#### 2.1 Frame Buffer

Build-in Buffer RAM

#### 2.2 Host Interface

- Support 8080/6800 8/16-bit asynchronous parallel bus interface

- Provide xnwait event to extend MPU cycle

- Support serial host Interface. Ex. IIC, 3/4-wire SPI

- Mirror and rotation functions are available for image data writes.

#### 2.3 Display Input Data Formats

- 1bpp: monochrome data (1-bit/pixel)

- 8bpp: RGB 3:3:2 (1-byte/pixel)

- 16bpp: RGB 5:6:5 (2-byte/pixel)

- 24bpp: RGB 8:8:8 (3-byte/pixel or 4-byte/pixel)

- Index 2:6 (64 index colors/pixel with opacity attribute)

- $\alpha$ RGB 4:4:4:4 (4096 colors/pixel with opacity attribute)

#### 2.4 Display Mode

Configurable digital TFT output: 24-bit TFT output / 18-bit TFT output / 16-bit TFT output

#### 2.5 Support Various Panel Resolution

- Support panel's resolution up-to 800x480 or 480x800, 16bpp

- Support panel's resolution up-to 640x480 or 480x640, 24bpp

#### 2.6 Display Features

- Provide 4 User-defined 32x32 pixels Graphic Cursor

- Display Window

The display window is defined by the size of the LCD display. Complete or partial updates to the display window are done through canvas image's setting. The active window size and start position are specified in 8 pixel resolution (horizontal) and 1 line resolution (vertical). Window coordinates are referenced to top left corner of the display window (even when flip is enabled or rotate text, no host side translation is required).

Picture-in-Picture (PIP) display

Two PIP windows are supported. Enabled PIP windows are always displayed on top of Main window. The PIP windows sizes and start positions are specified in 4 pixel resolution (horizontal) and 1 line resolution (vertical). Image scrolling can be performed by changing the start address of a PIP window. The PIP1 window is always on top of PIP2 window.

Wake-up display

Wake-up display is available to show the display data quickly which data is stored in Buffer RAM. This feature is used when returning from the Standby mode or Suspend mode.

Vertical Flip display

Vertical Flip display functions are available for image data reads. PIP window will be disabled if flip display function enable.

Color Bar Display

It could display color bar on panel and need not Buffer RAM. Default resolution is 640 dots by 480 dots.

#### 2.7 Initial Display

• Embed a tiny processor and use to show display data which stored in the serial flash and need not external MPU participate. It will auto execute after power-on, until program execute complete then handover control rights to external MPU. It supports 12 instructions. They are:

| - 11                                        | •                      |

|---------------------------------------------|------------------------|

| EXIT: Exit instruction (00h/FFh)            | one byte instruction   |

| NOP: NOP instruction (AAh)                  | one byte instruction   |

| EN4B: Enter 4-Byte mode instruction (B7h)   | one byte instruction   |

| EX4B: Exit 4-Byte mode instruction (E9h)    | one byte instruction   |

| STSR: Status read instruction (10h)         | two bytes instruction  |

| CMDW: Command write instruction (11h)       | two bytes instruction  |

| DATR: Data read instruction (12h)           | two bytes instruction  |

| DATW: Data write instruction (13h)          | two bytes instruction  |

| REPT: Load repeat counter instruction (20h) | two bytes instruction  |

| ATTR: Fetch Attribute instruction (30h)     | two bytes instruction  |

| JUMP: Jump instruction (80h)                | five bytes instruction |

| DJNZ: Decrement & Jump instruction (81h)    | five bytes instruction |

|                                             |                        |

#### 2.8 Block Transfer Engine (BTE)

- 2D BitBLT Engine

- Copy with ROP & color expansion

- Solid fill & Pattern fill

- Provide User-defined Patterns with 8x8 pixels or 16x16 pixels

- Opacity (Alpha-Blend) control

It allows two images to be blended to create a new image which can **then** be displayed using a PIP window. The processing speed of Alpha-blend function varies depending on the image size. Optionally, a single input image can be processed.

- Chroma-keying function: Mixes images with applying the specified RGB color according to transparency rate.

- Window Alpha-blending function: Mixes two images according to transparency rate in the specified region (fade-in and fade-out functions are available).

- Dot Alpha-blending function: Mixes images according to transparency rate when the target is a graphics image in the RGB format.

#### 2.9 Geometric Drawing Engine

Draw dot, Line, Curve, Circle, Ellipse, Triangle, Square & Circular Square

#### 2.10 SPI Master Interface

#### 2.10.1 Text Features

- Embedded 8x16,12x24,16x32 Character Sets of ISO/IEC 8859-1/2/4/5.

- Supporting Genitop Inc. UNICODE/BIG5/GB etc. Serial Character ROM with 16x16/24x24/32X32 dots Font Size. The supporting product numbers are GT21L16T1W, GT30L16U2W, GT30L24T3Y, GT30L24M1Z, and GT30L32S4W, GT20L24F6Y, GT21L24S1W.

- User-defined Characters support half size (8x16/12x24/16x32) & full size

- Programmable Text Cursor for Writing with Character

- Character Enlargement Function X1, X2, X3, X4 for Horizontal/Vertical Direction

- Support Character 90 degree Rotation

#### 2.10.2 DMA function

Support direct data transfer from external serial flash to frame buffer

#### 2.10.3 General SPI master

- Compatible with Motorola's SPI specifications

- 16 bytes entries deep read FIFO

- 16 bytes entries deep write FIFO

- Interrupt generation after Tx FIFO empty and SPI Tx/Rx engine idle

#### 2.11 IIC Interface

- IIC master interface

- For the expand I/O device, external touch screen controller for panel control

- Support Standard mode (100kbps) and Fast mode (400kbps)

#### 2.12 PWM Timer

- Two 16-bit timers

- One 8-bit pre-scalars & One 4-bit divider

- Programmable duty control of output waveform (PWM)

- Auto reload mode or one-shot pulse mode

- Dead-zone generator

#### 2.13 Key-scan Interface

- Support up-to 5x5 key matrix (share with the GPIO pin)

- Programmable scan period

- Support long Key & repeat key

- Support up to 2 keys are pressed simultaneously

Note: Restricted support 3-keys are pressed simultaneously (3-keys cannot form 90°)

- Support Key-Scan Wakeup function

#### 2.14 Power Saving

- Support 3 kind of power saving mode

- Standby mode, Suspend mode & Sleep mode

- It may wakeup by host, key & external event

#### 2.15 Clock Source

- Embedded programmable PLL for system core clock, LCD panel scan clock and the Buffer RAM clock

- Single crystal clock input: (XI/XO: 10-15MHz)

- Internal system clock (Maximum 80MHz)

- Buffer RAM clock (Maximum 80MHz)

- LCD panel scan clock (Maximum 40MHz)

#### 2.16 Reset

- Accept external hardware reset to synchronize with system

- Software command reset

#### 2.17 Power Supply

- I/O voltage: 3.3V +/- 0.3V

- Embedded 1.2V LDO for core power

#### 2.18 Package

- LQFP-128

- Operation temperature: -40<sup>°</sup>C ~ 85<sup>°</sup>C

### 3. Symbol and Package

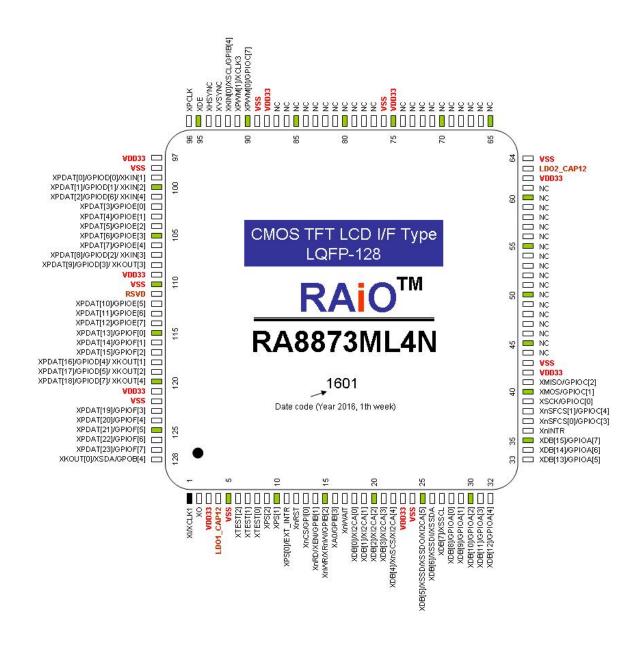

#### 3.1 RA8873M Symbol & Pin Assignment

Figure 3-1

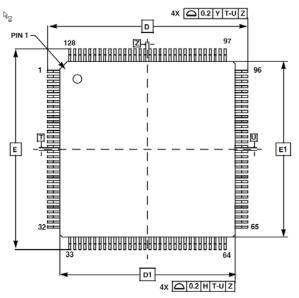

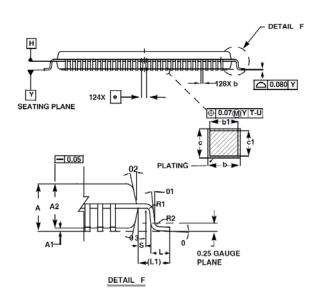

#### 3.2 Package Outline Dimensions

Q128.14x14

128 LEAD THIN PLASTIC QUAD FLATPACK PACKAGE .4 MM

PITCH

|        | MILLIMETERS |                |       |   |

|--------|-------------|----------------|-------|---|

| SYMBOL | MIN NOM MAX |                | NOTES |   |

| Α      | -           |                | 1.60  | - |

| A1     | 0.05        |                | 0.15  | - |

| A2     | 1.35        | 1.40           | 1.45  | - |

| b      | 0.13        | 0.16           | 0.23  | 4 |

| b1     | 0.13        | -              | 0.19  | - |

| С      | 0.09        | -              | 0.20  | - |

| c1     | 0.09        | -              | 0.16  | - |

| D      |             | 16 BSC         |       | - |

| D1     |             | 14 BSC         |       |   |

| E      |             | 16 BSC         |       |   |

| E1     |             | 14 BSC         |       | 3 |

| L      | 0.45        | 0.45 0.60 0.75 |       | - |

| L1     |             | 1.00 REF       |       | - |

| R1     | 0.08        | -              | -     | - |

| R2     | 0.08        | -              | 0.20  | - |

| S      | 0.20        | -              | -     | - |

| 0      | 0°          | 3.5°           | 7°    | - |

| 01     | 0°          | -              | -     | - |

| 02     | 11°         | 12°            | 13°   | - |

| 03     | 11°         | 11° 12° 13°    |       | - |

| N      | 128         |                |       | - |

| е      | 0.40 BSC    |                |       | - |

#### NOTES:

Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

Rev. 0 8/08

- 2. Dimensions and tolerances per AMSEY14.5M-1994.

- Dimensions D1 and E1 are excluding mold protrusion. Allowable protrusion is 0.25 per side. Dimensions D1 and E1 are exclusive of mold mismatch and determined by datum plane H.

- Dimension b does not include dambar protrusion.

Allowable dambar protrusion shall not cause the lead width to exceed the maximum b dimension by more than 0.08mm. Dambar cannot be located at the lower radius or the foot. Minimum space between protrusion and an adjacent lead is 0.07 mm.

Figure 3-2: RA8873M Package Outline Dimensions

# 4. Signal Description

# 4.1 Parallel Host Interface (25 signals)

| Pin Name       | Dir/Drv.    | Pin Description                                                                                                                                                                                                                                                                                                                                                  |

|----------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XDB[15:0]      | IO<br>(8mA) | Data Bus These are data bus for data transfer between parallel host and RA8873M. XDB[15:8] will become GPIO (GPIO-A[7:0]) if parallel host 8080/6800 16-bit data bus mode doesn't set. XDB[7:0] are multiplex with serial host signals if serial host mode set. Please refer to serial host interface section.                                                   |

| XA0            | I           | Command / Data Select Input The pin is used to select command/data cycle.  XA0 = 0, status read / command write cycle is selected.  XA0 = 1, data read / Write cycle is selected.                                                                                                                                                                                |

| XnCS           | I           | Chip Select Input Low active chip select pin. If host I/F set as serial host mode then this pin can be read from GPI-B0. With internal pull-high with resistor.                                                                                                                                                                                                  |

| XnRD<br>(XEN)  | I           | Enable/Read Enable When MPU interface (I/F) is 8080 series, this pin is used as XnRD signal (Data Read), active low. When MPU I/F is 6800 series, this pin is used as XEN signal (Enable), active high. If host I/F set as serial host mode then this pin can be read from GPI-B1. With internal pull-high with resistor.                                        |

| XnWR<br>(XRnW) | I           | Write/Read-Write When MPU I/F is 8080 series, this pin is used as XnWR signal (data write), active low. When MPU I/F is 6800 series, this pin is used as XRnW signal (data read/write control). Active high for read and active low for write. If host I/F set as serial host mode then this pin can be read from GPI-B2. With internal pull-high with resistor. |

| XnINTR         | O<br>(8mA)  | Interrupt Signal Output The interrupt output for host to indicate the status.                                                                                                                                                                                                                                                                                    |

| XnWAIT         | O<br>(8mA)  | Wait Signal Output When high, it indicates that the RA8873M is ready to transfer data. When low, then microprocessor is in wait state.                                                                                                                                                                                                                           |

| XPS[2:0]       | I           | Parallel /Serial Host I/F Select  00X: (parallel host) 8080 interface with 8/16-bit data bus  01X: (parallel host) 6800 interface with 8/16-bit data bus  100: (serial host) 3-Wire SPI  101: (serial host) 4-Wire SPI  11x: (serial host) IIC  Note:  If host I/F set as parallel host mode, then XPS[0] pin is external interrupt pin.                         |

# 4.2 Serial Host Interface (Multiplex with Parallel Host Interface)

| Pin Name                                                                                                                   | Dir/Drv.                                                        | Pin Description                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XSSCL<br>(XDB[7])                                                                                                          | SPI or IIC Clock XSSCL, 3-wire, 4-wire Serial or IIC I/F clock. |                                                                                                                                                                                                                          |

| XSSDI<br>XSSDA<br>(XDB[6])                                                                                                 | I                                                               | IIC data /4-wire SPI Data Input 3-wire SPI I/F: NC, please connect it to GND. 4-wire SPI I/F: XSSDI, Data input for serial I/F. IIC I/F: XSSDA, Bi-direction data for serial I/F                                         |

| XSSDO (XDR(51))  IO  3-wire SPI I/F: XSSD, Bi-direction data for serial I/4-wire SPI I/F: XSSDO, Data output for serial I/ |                                                                 | 3-wire SPI Data /4-wire SPI Data Output/IIC Slave Address Select 3-wire SPI I/F: XSSD, Bi-direction data for serial I/F 4-wire SPI I/F: XSSDO, Data output for serial I/F. IIC I/F: XIICA[5], IIC device address bit [5] |

| XnSCS<br>(XDB[4])                                                                                                          | ı                                                               | SPI Chip Select/IIC Slave Address Select XnSCS, Chip select pin for 3-wire or 4-wire serial I/F. IIC I/F: XIICA[4], IIC device address bit [4].                                                                          |

| XIICA[3:0]<br>(XDB[3:0])                                                                                                   |                                                                 | IIC I/F: IIC Slave Address Select.  XIICA[3:0], 3 4-wire SPI I/F: NC, please connect it to GND.  IIC I/F: IIC device address bit [3:0]                                                                                   |

## 4.3 Serial Flash or SPI master Interface (5 signals)

| Pin Name                  | Dir/Drv.    | Pin Description                                                                                                                                                                                                                                                                                                                    |  |  |

|---------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| XnSFCS0                   | IO<br>(8mA) | Chip Select 0 for External Serial Flash/ROM or SPI device SPI Chip select pin #0 for serial Flash/ROM or SPI device. * If SPI master I/F is disabled then it can be programmed as GPIO (GPIO-C3); default is GPIO-C3 input function.                                                                                               |  |  |

| XnSFCS1                   | IO<br>(8mA) | Chip Select 1 for External Serial Flash/ROM or SPI device SPI Chip select pin #1 for serial Flash/ROM or SPI device. * If SPI master I/F is disabled then it can be programmed as GPIO (GPIO-C4); default is GPIO-C4 input function. *auto pull-high in reset period if xtest[2:1] is not equal to 01b.                            |  |  |

| хѕск                      | IO<br>(8mA) | SPI Serial Clock Serial clock output for serial Flash/ROM or SPI device.  * If SPI master I/F is disabled then it can be programmed as GPIO (GPIO-C0); default is GPIO-C0 input function.                                                                                                                                          |  |  |

| XMOSI IO<br>(XSIO0) (8mA) |             | Master Output Slave Input Single mode: Data input of serial Flash/ROM or SPI device. For RA8873M, it is output. Dual mode: The signal is used as bi-direction data #0(SIO0). Only valid in serial flash DMA mode.  * If SPI master I/F is disabled then it can be programmed as GPIO (GPIO-C1); default is GPIO-C1 input function. |  |  |

| XMISO IO (8mA)            |             | Master Input Slave Output Single mode: Data output of serial Flash/ROM or SPI device. For RA8873M, it is input. Dual mode: The signal is used as bi-direction data #1(SIO1). Only valid in serial flash DMA mode.  * If SPI master I/F is disabled then it can be programmed as GPIO (GPIO-C2); default is GPIO-C2 input function. |  |  |

# 4.4 PWM Interface (2 signals)

| Pin Name Dir/Drv.       |             | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XPWM0                   | IO<br>(8mA) | PWM signal output 1 / Initial Display Enable Pull-high this pin will enable Initial Display function. This pin has internal pull-down in reset period to disable Initial Display function by default. i.e. after reset complete, internal pull-down resistor will be disabled. XPWM 0 output mode is decided by configuration register. If PWM function disabled then it can be programmed as GPIO (GPIO-C7), default is GPIO-C7 input function, or output core clock. |

| XPWM1 IO reg for out Wh |             | PWM signal output 2 / Clock 3 input (panel scan clock) When XTEST[0] set low: XPWM1 set as output mode & output function is decided by configuration register. It may normal XPWM1 function, oscillator clock output or error flag for Scan bandwidth insufficient or Memory access out of range. (or Iso clock output) When XTEST[0] set high: XPWM1 pin is external panel scan clock input                                                                           |

# 4.5 KEYSCAN Interface (10 signals)

| Pin Name           | Dir/Drv. | Pin Description                                                                                                                                                                                                         |

|--------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XKIN[4:0] I        |          | Keypad Data Line or GPIs (General Purpose Input) Keypad data inputs (Default), with internal pull-up resister. XKIN[0] also has IIC master's XSCL function. In RA8873M, XKIN [4:1] are share with XPDAT & GPIO-D.       |

| XKOUT[4:0] O (2mA) |          | Keypad Strobe Line or GPOs (General Purpose Output) Keypad matrix strobe lines outputs with open-drain. (Default). XKOUT[0] also has IIC master's XSDA function. In RA8873M, XKOUT [4:1] are share with XPDAT & GPIO-D. |

# 4.6 LCD Panel Digital Interface (28 signals)

| Pin Name        | Dir/Drv.    | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                       |                                                                                                                                                                                       |                                                                                                  |    |

|-----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----|

| XPCLK           | O<br>(8mA)  | Panel scan Clock Generic TFT interface signal for panel scan clock. It derives from SPLL.                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                       |                                                                                                                                                                                       |                                                                                                  |    |

| XVSYNC          | O<br>(4mA)  | VSYNC Pulse<br>Generic TFT into                                                                                                                                                                                                                                                                                                                                                                                      | erface signa                                                                                                                                                                                                                                                  | I for vertical                                                                                                                                                                                                        | synchronous                                                                                                                                                                           | s pulse.                                                                                         |    |

| XHSYNC          | O<br>(4mA)  | HSYNC Pulse<br>Generic TFT into                                                                                                                                                                                                                                                                                                                                                                                      | erface signa                                                                                                                                                                                                                                                  | l for horizon                                                                                                                                                                                                         | tal synchrono                                                                                                                                                                         | ous pulse.                                                                                       |    |

| XDE             | O<br>(4mA)  | Data Enable<br>Generic TFT into                                                                                                                                                                                                                                                                                                                                                                                      | erface signa                                                                                                                                                                                                                                                  | l for data va                                                                                                                                                                                                         | lid or data en                                                                                                                                                                        | nable.                                                                                           |    |

| XPDAT<br>[23:0] | IO<br>(4mA) | LCD Panel Data TFT LCD data b 65K/262K/16.7N corresponding F  Pin Name TFT output Setting XPDAT[0] XPDAT[1] XPDAT[2] XPDAT[3] XPDAT[4] XPDAT[5] XPDAT[6] XPDAT[6] XPDAT[6] XPDAT[7] XPDAT[8] XPDAT[10] XPDAT[10] XPDAT[11] XPDAT[12] XPDAT[12] XPDAT[13] XPDAT[14] XPDAT[15] XPDAT[15] XPDAT[16] XPDAT[16] XPDAT[17] XPDAT[18] XPDAT[19] XPDAT[19] XPDAT[20] XPDAT[21] XPDAT[23] *unused pins can Default is 18bpp f | a Bus bus output for A color depth CGB bus for  11b (GPIO)  GF GF GPIO-D6 GPIO-E0 GPIO-E1 GPIO-E2 GPIO-E3 GPIO-E4 GPIO-E5 GPIO-E5 GPIO-F0 GPIO-F1 GPIO-F2 GPIO-F1 GPIO-F2 GPIO-F1 GPIO-F2 GPIO-F3 GPIO-F3 GPIO-F5 GPIO-F5 GPIO-F5 GPIO-F5 GPIO-F7 be programm | r source driven by register different set Digital TF 10b (16-bit) PIO-DO/ XKI PIO-DO/ XKIN[4] B0 B1 B2 B3 B4 PIO-D2/ XKI PIO-D3/ XKO G0 G1 G2 G3 G4 G5 O-D4/ XKO O-D5/ XKO O-D5/ XKO UT[4] R0 R1 R2 R3 R4 ed as GPIO- | ver. RA8873N setting; user ting.  T Interface  01b (18-bit) N[1] N[2]  B0  B1  B2  B3  B4  B5 N[3] UT[3]  G0  G1  G2  G3  G4  G5  UT[1] UT[2]  R0  R1  R2  R3  R4  R5  D/E/F(default) | 00b (24-bit) B0 B1 B2 B3 B4 B5 B6 B7 G0 G1 G2 G3 G4 G5 G6 G7 R0 R1 R2 R3 R4 R5 R6 R7 or XKIN/XOU | T. |

# 4.7 Clock, Reset & Test Mode (6 signals)

| Pin Name                                                                                           | Dir/Drv. | Pin Description                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| XI (XCLK1)  Crystal Oscillator ran When XTEST[0] set connected to exter RA8873M. When XTEST[0] set |          | Crystal Input Pin / Clock 1 input (core clock)  Crystal Oscillator range is 10MHz ~ 15MHz.  When XTEST[0] set low, this input pin for internal crystal circuit. It should be connected to external crystal circuit. That will generate the clock for RA8873M.  When XTEST[0] set high, this pin is external clock 1 input.  Suggested OSC frequency is 11.0592MHz. |  |  |

| хо                                                                                                 | 0        | Crystal Output Pin This is an output pin for internal crystal circuit. It should be connected to external crystal circuit.                                                                                                                                                                                                                                         |  |  |

| XnRST                                                                                              | I/OC     | Reset Signal input To avoid noise interfere XnRST signal and cause fake reset behavior, external XnRST level will be admitted only if it keep its signal level at least 256 OSC clocks.                                                                                                                                                                            |  |  |

| 0: Normal mode, Use internal PLL clock.                                                            |          | Internal pull down. For chip test function, should be connected to GND for normal operation.                                                                                                                                                                                                                                                                       |  |  |

| XTEST[2:1]                                                                                         | I        | Chip Test Mode 00: normal mode 01: Force SPI master I/F pin floating (for in-system-programming) 1X: RESERVED                                                                                                                                                                                                                                                      |  |  |

#### 4.8 Power and Ground

| Pin Name                 | Dir/Drv. | Pin Description                                        |  |

|--------------------------|----------|--------------------------------------------------------|--|

| LDO1_CAP12<br>LDO2_CAP12 | _        |                                                        |  |

| VDD33                    | Р        | IO VDD<br>3.3V IO power input.                         |  |

| vss                      | Р        | GND IO Cell/Core ground signal                         |  |

| RSVD                     | Р        | Reserved Suggest to connect a 1uF capacitor to ground. |  |